Giao tiếp với SDRAM

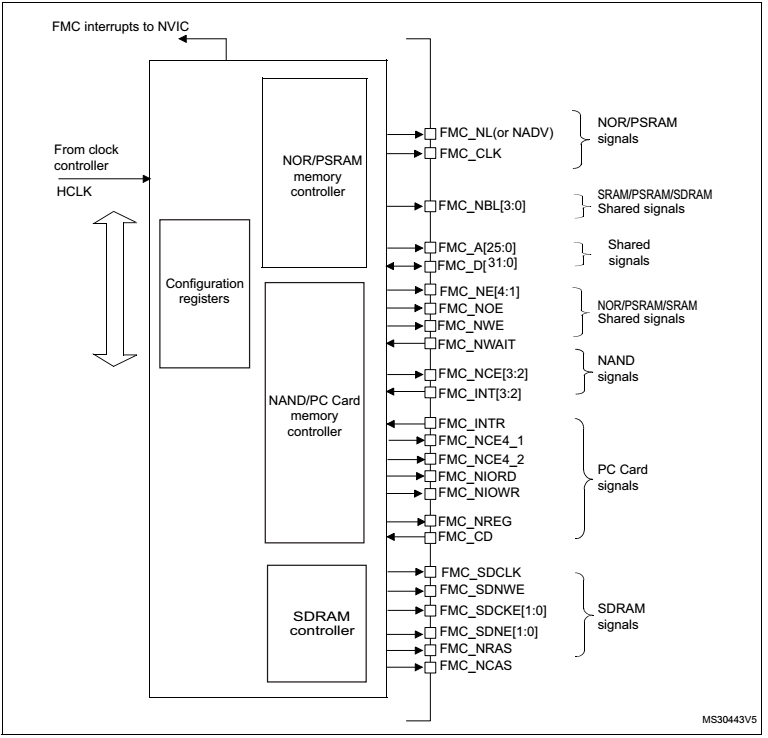

Trên MCU STM32F429 có bộ Flexible memory controller (FMC) gồm có 3 bộ điều khiển:

- Bộ điều khiển bộ nhớ NOR/PSRAM

- Bộ điều khiển NAND/PC Card

- Bộ điều khiển Synchronous DRAM

Sơ đồ khối

FMC gồm có 4 khối chính:

- AHB interface (kể cả các thanh ghi cấu hình FMC)

- Bộ điều khiển NOR Flash/PSRAM/SRAM

- Bộ điều khiển NAND Flash/PC Card

- Bộ điều khiển SDRAM

- Interface ngoại vi

Bản đồ địa chỉ thiết bị ngoại vi

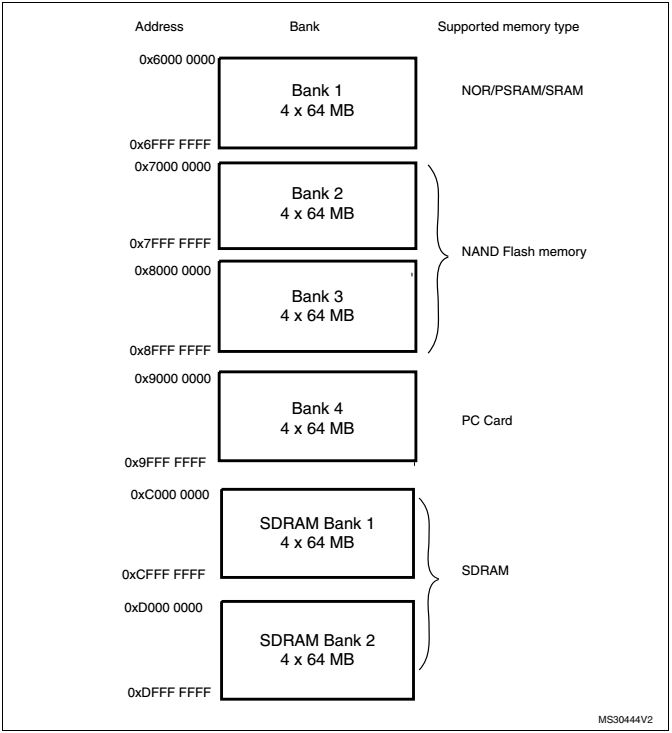

Nhìn từ FMC, bộ nhớ ngoại vi được chia thàng 6 bank kích thước cố định của mỗi 256 Mbyte.

- Bank 1 được sử dụng làm địa chỉ lên tới 4 thiết bị bộ nhớ NOR Flash hoặc PSRAM.

- Bank 2 và 3 được sử dụng làm địa chỉ các thiết bị bộ nhớ NAND Flash (1 thiết bị trên bank)

- Bank 4 được sử dụng làm địa chỉ PC Card

- Bank 5 và 6 được sử dụng làm địa chỉ các thiết bị SDRAM (1 thiết bị trên bank)

Cho mỗi bank loại bộ nhớ được sử dụng có thể được cấu hình bởi người dùng qua thanh ghi Cấu hình.

Sơ đồ địa chỉ SDRAM

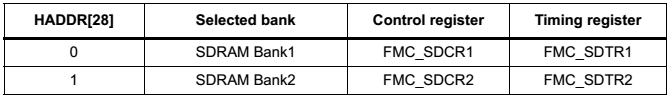

Bit HADDR[28] được sử dụng để chọn 1 trong 2 bank bộ nhớ

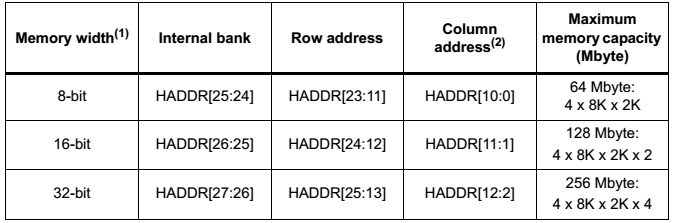

Bảng dưới đây trình bày sơ đồ SDRAM cho 1 hàng 13-bit, 1 cột 11-bit và cấu hình 4 bank nội.

Bảng dưới đây trình bày sơ đồ SDRAM cho 1 hàng 13-bit, 1 cột 11-bit và cấu hình 4 bank nội.

(1): khi giao tiếp với một bộ nhớ 16-bit, bên trong FMC sử dụng đường địa chỉ AHB HADDR[11:1] để tạo ra địa chỉ ngoại vi. Khi giao tiếp với bộ nhó 32-bit, bên trong FMC sử dụng đường địa chỉ HADDR[12:2] để tạo địa chỉ ngoại vi. Dù bất cứ bộ nhớ nào, FMC_A[0] cũng kết nối với với địa chỉ bộ nhớ ngoại vi A[0].

(2): AutoPrecharge không được hỗ trợ, FMC_A[10] phải được kết nối với địa chỉ A[10] nhưng nó sẽ luôn ở mức 'thấp'.

Đặc điểm chính của bộ điều khiển SDRAM

- 2 bank SDRAM với việc cấu hình độc lập.

- Độ rộng bus dữ liệu 8, 16, 32 bit.

- Hàng địa chỉ 13-bit, cột địa chỉ 11-bit, 4 bank nội: 256MB, 128 MB, 64 MB.

- Truy cập theo word, half-word, byte.

- Clock SDRAM có thể sử dụng HCLK/2 hoặc HCLK/3

- Tự động quản lý đường biên hàng và bank.

- Truy cập multibank ping-pong.

- Có thể lập trình được các thành phần thời gian.

- Tự động hoạt động làm tươi với tốc độ làm tươi có thể lập trình được.

- Chế độ tự làm tươi.

- Chế độ power-down

- Khởi tạo power-up SDRAM bằng phần mềm.

- Bộ nhớ cache READ FIFO với độ sâu của 6 đường x 32-bit

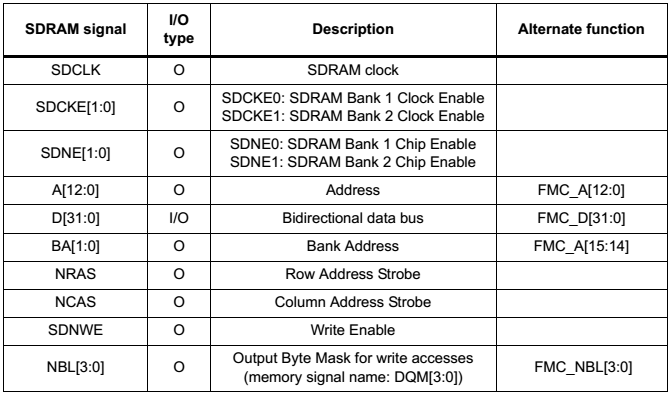

Các tín hiệu giao tiếp bộ nhớ ngoài SDRAM

Khi khởi động, các pin I/O SDRAM được sử dụng giao tiếp bộ điều khiển FMC SDRAM với các thiết bị ngoại vi SDRAM phải được cấu hình bởi người sử dụng. Các pin I/O bộ điều khiển SDRAM không sử dụng có thể dùng cho các mục đích khác.

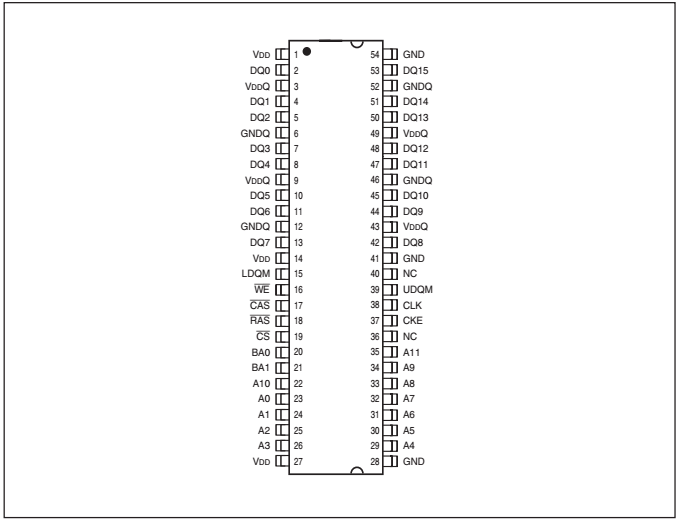

IC SDRAM

IC SDRAM được sử dụng là IS42S16400J 64-MBit, tần số xung clock 143 MHZ.

| Pin | Function |

|---|---|

| A0-A11 | ngõ vào địa chỉ hàng được lấy mẫu trong khi có lệnh ACTIVE và lệnh READ/WRITE để chọn một vùng bộ nhớ trong bank tương ứng. A10 được lấy mẫu trong lúc lệnh PRECHARGE để xác định nếu mọi bank được nạp lại (A10 mức cao) hoặc bank được chọn bởi BA0, BA1 (mức thấp) |

| A0-A7 | Ngõ vào địa chỉ cột |

| BA0, BA1 | Địa chỉ chọn bank: BA0 và BA1 xác định bank đó ACTIVE, READ, WRITE hay PRECHARGE được đưa vào |

| DQ0 đến DQ15 | Data I/O |

| CLK | CLK là ngõ vào xung clock master cho thiết bị này. Trừ CKE ra, mọi ngõ vào thiết bị này được đồng bộ khi có xung cạnh lên CLK |

| CKE | xung cho phép định rõ khi nào ngõ vào CLK được cho phép. Xung cạnh lên tiếp theo của CLK sẽ có hiệu lực nếu CKE mức cao và ngược lại. CKE là ngõ vào không đồng bộ |

| CS | Lựa chọn chip xác định khi nào ngõ vào lệnh được cho phép trong thiết bị. Ngõ vào lệnh được cho phép khi CS mức thấp và ngược lại. |

| RAS | Lệnh phân tích địa chỉ hàng |

| CAS | Lệnh phân tích địa chỉ cột |

| WE | Cho phép ghi |

| LDQM | x16 Lower Byte, Input/Output Mask |

| UDQM | x16 Upper byte, Input/Output Mask |

| VDD | Nguồn |

| GND | Đất |

| VDDQ | Nguồn cho I/O pin |

| GNDQ | Đất cho I/O pin |